Trung tâm đào tạo thiết kế vi mạch Semicon

Nội Dung

I. Giới thiệu về nguồn gốc JTAG

Từ trước đến giờ có lẽ chúng ta nhầm tưởng JTAG là công cụ được sinh ra để phục vụ cho việc nạp chíp và debug phần mềm, nhưng thực sự JTAG (Joint Test Action Group) được làm ra với mục đích phục vụ cho việc test PCB ( sử dụng boundary scan). Ngày nay công cụ này được chuẩn hóa bở IEEE 1149.1 và thêm một số chức năng cho việc debug phầm mềm hệ thống.

Bạn đang xem: Trung tâm đào tạo thiết kế vi mạch Semicon

JTAG là một phương pháp test PCB được một nhóm kỹ sư Harry Wardrop đề xuất đầu tiên vào năm 1985. Sự ra đời của công cụ này xuất phát từ tính phức tạp của phần cứng của hệ thống ngày càng cao. Hệ thống không chỉ là 1 chíp và là nhiều chíp, PCB không chỉ 1 lớp, 2 lớp mà là nhiều lớp. Chính vì thế người ta không thể dùng đầu dò để kiểm tra hệ thống. JTAG giúp giải quyết những khó khăn về các lỗi trong công nghiệp điện tử như : Kiểm tra các mối tiếp xúc giữa chíp và PCB. Một ví dụ điển hình là các chíp có dạng vỏ đặt biệt (BGA). Tất nhiên phương pháp chụp Xray có thể giải quyết điều này, tuy nhiên không hiệu quả về mặc kinh tế vì chi phí cao, thời gian thực hiện lâu dài.

Các chíp hiện đại hầu như điều có tích hợp JTAG bên trong, điển hình như FPGA, ARM CPU, các chíp ngoại vi transceiver DP8384x… Việc tích hợp JTAG vào chíp làm tăng chi phí silicon tuy nhiên rất hữu ích cho việc test khi mà số lượng sản phẩm có giá trị từ hàng ngàn trở lên.

II. Nguyên lý cơ bản về JTAG.

Theo đặt tính về điện, JTAG bao gồm các thành phần sau:

1.TDI (Test Data In)

2.TDO (Test Data Out)

3.TCK (Test Clock)

4.TMS (Test Mode Select)

5.TRST (Test Reset) optional.

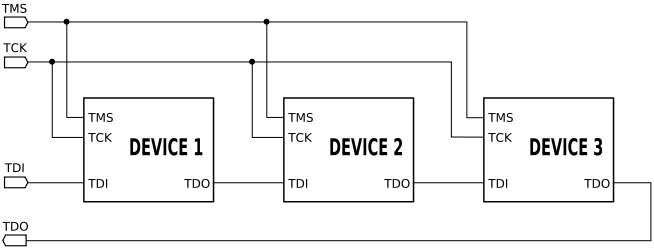

Các tín hiệu này được thiết kế với mục đích không chỉ test cho 1 chíp mà có thể test cho 1 loạt các chíp, khi đó các chíp này được kết nối theo một chuỗi (daisy-chained) theo sơ đồ sau:

Đối với từng thiết bị, dữ liệu được đưa vào đường TDI và dữ liệu ra là TDO. Các dữ liệu này được đồng bộ bởi tín hiệu TCK. TMS xác lập mode hoạt động cho JTAG ( thay đổi trạng thái), ngoài ra người ta còn có thể thêm vào 1 vài đường TRST và SRST nhằm thực hiện reset JTAG TAP controller và reset toàn hệ thống.

Kế tiếp, tìm hiểu thêm kết cấu của 1 con chíp sau khi đã tích hợp JTAG core bên trong:

JTAG core bao gồm TAP controller, một số thanh ghi IR (Instruction Register), BYPASS, ID và một số thanh ghi khác. Thành phần thứ hai bao gồm các boudary scan cells. Các cell này kết nối trực tiếp với IO pin của con chíp, có thể trực tiếp điều khiển mức logic của các IO pin này mà không phải thông qua Core Logic của chíp.

Cách hoạt động của JTAG:

TAP controller hoạt động như một máy trạng thái (state machine), bao gồm 16 trạng thái, và chỉ có thể được thay đổi thông qua sự cho phép của tín hiệu TMS

Giá trị 0, 1 biểu thị sự thay đổi của tín hiệu TMS, ví dụ: Giả sử ta ở trạng thái Select DR-Scan, nếu TMS = 0, khi có sự thay đổi của xung clock thì trạng thái sẽ được chuyển sang Capture-DR. Để JTAG hoạt động đúng, chương trình điều khiển phải nắm giữ được trạng thái hiện tại của JTAG. Khi chíp được bật nguồn điện, trạng thái của TAP controller là bất định (1 trong 16 trạng thái trên). Tuy nhiên phần mềm điều khiển có thể đưa TAP controller về trạng thái Test-logic-Reset bằng cách giữ TMS = 1 và thay đổi 5 lần xung TCK.

Ví dụ: Chương trình điều khiển di chuyển TAP controller đến trạng thái Shift-IR sau khi bật nguồn cho chip

// first sync everybody to the test-logic-reset state

for(i=0; i<5; i++) JTAG_clock(TMS);

// now that everybody is in a known and identical state, we can move together to another state

// let’s go to Shift-IR

JTAG_clock(0);

JTAG_clock(TMS);

JTAG_clock(TMS);

JTAG_clock(0);

JTAG_clock(0);

IR-Register

Mỗi loại chíp sẽ có một tập hợp lệnh khác nhau. Tương ứng, TAP controller cũng có 1 thanh ghi IR-Register phục vụ cho việc thực thi các lệnh này. Các lệnh này được các nhà sản xuất chíp cung cấp ở dạng file BSDL (Boundary Scan Description Language), thực chất là 1 file VHDL mô tả cách thức JTAG (theo chuẩn IEEE 1149.1) thực hiện điều khiển con chíp. Để có được các file trên, có thể tham khảo vào các trang web của các hãng sản xuất chíp và download về (miễn phí).

Tùy từng loại chíp, chiều dài của IR có thể khác nhau, ví dụ sau biểu thị CPU có chiều dài bit của IR là 5, FPGA là 10, kết nối 2 chip thông qua sơ đồ daisy-chained. Dữ liệu được truyền thông qua TDI và TDO.

Về phía chương trình điều khiển (PC) IR được hiểu là 15 bits long. Sau khi qua 15 lần dịch bit (15 xung clock) thì thanh ghi IR của CPU và FPGA được điền đầy đủ. Nếu ta đưa thêm 15 xung clock nữa, thì giá trị IR của CPU và FPGA sẽ được read back về PC thông qua TDO. Lưu ý rằng, việc điền thông tin vào IR được thực hiện ở trạng thái Shift-IR.

Ví dụ : Chương trinh ghi vào IR CPU giá trị 00100 và ghi vào IR FPGA giá trị 0000000010 :

// Because the bits are shifted through in a chain, we must start sending the data for the device that is at the end of the chain

// so we send the 10 FPGA IR bits first

JTAG_clock(0);

JTAG_clock(1);

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(0);

// then send the 5 CPU IR bits

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(1);

JTAG_clock(0);

JTAG_clock(0 | TMS); // last bit needs to have TMS active (to exit shift-IR)

Ở ví dụ trên, IR CPU có 5 bits long, có nghĩa là support tối đa 32 lệnh, IR FPGA có 10 bits long, support tối đa 1024 lệnh. Tuy nhiên thông thường các thiết bị chỉ áp dụng một vài lệnh cơ bản mà thôi, điển hình như:

BYPASS

EXTEST

SAMPLE/PRELOAD

Xem thêm : Tattoo là gì? Những điều cần lưu ý khi xăm hình và cách xóa tattoo

IDCODE (not mandatory but very often implemented)

Để xem danh sách các lệnh này, chúng ta có thể tham khảo datasheet của thiết bị hoặc file BSDL.

SCAN, QUERY THE JTAG CHAIN:

Đếm số thiết bị trên chuỗi hệ thống:

Lệnh BYPASS được thiết lập khi các giá trị bit của thanh ghi IR là 1 và khi đó thanh ghi DR hoạt động như một delay flip-flop. Có nghĩa là đường đi của tín hiệu TDI-TDO chíp sẽ bị trễ 1 xung clock. Lệnh này cho phép ta đếm số lượng chíp trên 1 chuỗi JTAG. Đầu tiên ta thực hiện lệnh BYPASS trên tất cả các chíp bằng cách điền toàn bộ giá trị 1 vào thanh ghi IR của chúng. Sau đó chuyển TAP controller sang trạng thái Shift-DR, đưa giá trị 1 vào tín hiệu TDI và thực hiện thay đổi xung CLK cho đến khi nhận được giá trị 1 trên tín hiệu TDO. Khi đó tổng số xung CLK biểu thị số chíp hiện diện trên chuỗi JTAG.

Ta xét ví dụ sau :

// go to reset state

for(i=0; i<5; i++) JTAG_clock(TMS);

// go to Shift-IR

JTAG_clock(0);

JTAG_clock(TMS);

JTAG_clock(TMS);

JTAG_clock(0);

JTAG_clock(0);

// Send plenty of ones into the IR registers

// That makes sure all devices are in BYPASS!

for(i=0; i<999; i++) JTAG_clock(1);

JTAG_clock(1 | TMS); // last bit needs to have TMS active, to exit shift-IR

// we are in Exit1-IR, go to Shift-DR

JTAG_clock(TMS);

JTAG_clock(TMS);

JTAG_clock(0);

JTAG_clock(0);

// Send plenty of zeros into the DR registers to flush them

for(i=0; i<1000; i++) JTAG_clock(0);

// now send ones until we receive one back

for(i=0; i<1000; i++) if(JTAG_clock(1)) break;

nbDevices = i;

printf(“There are %d device(s) in the JTAG chainn”, nbDevices);

BOUNDARY-SCAN:

Với boundary-scan, chúng ta có thể ghi, đọc trạng thái IO pin của chíp (ngay cả chíp đang hoạt động).

LỆNH SAMPLE:

Lệnh cho phép đọc trạng thái của các IO pin trên chíp. Trước tiên ta tìm hiểu sơ qua đặt tính mô tả file BSDL của chíp Cyclone EP1C3 (Altera TQFP 100 pins package)

attribute INSTRUCTION_LENGTH of EP1C3T100 : entity is 10;

attribute INSTRUCTION_OPCODE of EP1C3T100 : entity is

“BYPASS (1111111111), “&

“EXTEST (0000000000), “&

“SAMPLE (0000000101), “&

“IDCODE (0000000110), “&

“USERCODE (0000000111), “&

“CLAMP (0000001010), “&

“HIGHZ (0000001011), “&

“CONFIG_IO (0000001101)”;

attribute INSTRUCTION_CAPTURE of EP1C3T100 : entity is “0101010101”;

attribute IDCODE_REGISTER of EP1C3T100 : entity is

“0000”& -4-bit Version

“0010000010000001”& -16-bit Part Number (hex 2081)

“00001101110”& -11-bit Manufacturer’s Identity

“1”; -Mandatory LSB

attribute BOUNDARY_LENGTH of EP1C3T100 : entity is 339;

+ Chiều dài IR 10 bits long

+ Các lệnh bao gồm BYPASS, EXTEST, SAMPLE, IDCODE, USERCODE, CLAMP, HIGHZ, CONFIG_IO

+ IDCODE : 00001101110b = 0x6E

Xem thêm : Fieldbus Là Gì ? » Thuận Nhật Các Loại Truyền Thông Công Nghiệp

+ Chiều dài boundary-scan chain 339 bits long.

Chiều dài boundary-scan chain là 339 bit, tuy nhiên không đồng nghĩa chíp có 339 pin. Mỗi pin tương ứng 1 IO pad trên IC die, mỗi IO pad có thể chiếm từ 1, 2 hoặc 3 bit của boundary-scan chain bởi vì mỗi pin của chíp có thể mang một số thuộc tính như input, output, tri-state…

attribute BOUNDARY_REGISTER of EP1C3T100 : entity is

-BSC group 0 for I/O pin 100

“0 (BC_1, IO100, input, X),” &

“1 (BC_1, *, control, 1),” &

“2 (BC_1, IO100, output3, X, 1, 1, Z),” &

-BSC group 1 for I/O pin 99

“3 (BC_1, IO99, input, X),” &

“4 (BC_1, *, control, 1),” &

“5 (BC_1, IO99, output3, X, 4, 1, Z),” &

…

…

…

-BSC group 112 for I/O pin 1

“336 (BC_1, IO1, input, X),” &

“337 (BC_1, *, control, 1),” &

“338 (BC_1, IO1, output3, X, 337, 1, Z)” ;

Ở ví dụ cho ta thấy bit 3 biểu thị trạng thái của pin99, bit 4 cho control, bit 5 cho output…

Đoạn code sau thực hiện việc đọc thanh ghi boundary-scan và hiển thị trạng thái của pin99

// go to reset state

for(i=0; i<5; i++) JTAG_clock(TMS);

// go to Shift-IR

JTAG_clock(0);

JTAG_clock(TMS);

JTAG_clock(TMS);

JTAG_clock(0);

JTAG_clock(0);

// Assuming that IR is 10 bits long,

// that there is only one device in the chain,

// and that SAMPLE code = 0000000101b

JTAG_clock(1);

JTAG_clock(0);

JTAG_clock(1);

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(0);

JTAG_clock(0 or TMS); // last bit needs to have TMS active, to exit shift-IR

// we are in Exit1-IR, go to Shift-DR

JTAG_clock(TMS);

JTAG_clock(TMS);

JTAG_clock(0);

JTAG_clock(0);

// read the boundary-scan chain bits in an array called BSB

JTAG_read(BSB, 339);

printf(“Status of pin 99 = %dn, BSB[3]);

Nguồn: 25giay.vnttp://www.fpga4fun.com

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được ChúngHãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 – 0938.838.404 (Mr Long)

Nguồn: https://25giay.vn

Danh mục: Hỏi Đáp